10+ soc block diagram

Politically Europe is divided into about fifty sovereign states of which Russia is the largest and most populous spanning 39 of the continent and comprising. Skylake succeeded the short-lived Broadwell which experienced severe delays.

Odroid Go Ultra Portable Gaming Console And Devkit Coming Soon With Amlogic S922x Soc Cnx Software

Cortex-A9 MPU Subsystem Block Diagram and System Integration 103.

. The sanctions can be either comprehensive or selective using the blocking of assets and trade restrictions to accomplish foreign policy and national security goals. Si4010 with an External Crystal in a 4-button RKE System. RSL10 is a Bluetooth 52 multi-protocol radio System on Chip SoC bringing ultra-low-power Bluetooth Low Energy to wireless applications.

Cortex-A9 MPU Subsystem Register Implementation. They can grow larger and you may notice them more over time. The term matrix-assisted laser desorption ionization MALDI was coined in 1985 by Franz Hillenkamp Michael Karas and their colleagues.

Varicoceles can exist on both sides at the same time but this is rare. The above block diagram consists of the battery pack battery charger dc-dc converter air conditioner etc. In computer engineering a hardware description language HDL is a specialized computer language used to describe the structure and behavior of electronic circuits and most commonly digital logic circuits.

The AGC provided computation and electronic interfaces for guidance navigation and control of the spacecraft. Where is OFACs country list. Skylake is the Architecture phase as part of Intels PAO model.

The Apollo4 SoC family is the 4 th generation system processor solution built upon the Ambiq. Block Diagram for the Ultra-Low Power Apollo4 SoC. The SARS-CoV-2 nucleocapsid N protein is an abundant RNA-binding protein critical for viral genome packaging yet the molecular details that underlie this process are poorly understood.

Offering the industrys lowest power consumption RSL10 enables advanced wireless features while optimizing system size and battery life. 9712 orders delivered before the deadline. The block directions red arrows α 63 0 and 63 are obtained from b.

A single AI Tensor Block achieves up to 15X more INT8 2 throughput than standard Intel Stratix 10 FPGA DSP Block. The microarchitecture was developed by. The Si4010 is a fully integrated crystal-less CMOS SoC RF transmitter with an embedded CIP-51 8051 MCU.

Varicoceles form during puberty. 3a are small 10 4 m s 1 and a linear extrapolation indicates that a current density as large as for DWs 10 11 to 10 12 A m 2 would be. And cooling of the battery pack.

The tryptophan was absorbing the laser energy and helping to. These researchers found that the amino acid alanine could be ionized more easily if it was mixed with the amino acid tryptophan and irradiated with a pulsed 266 nm laser. This is because the male anatomy is not the same on both sides.

OFAC administers a number of different sanctions programs. WebSocket is a computer communications protocol providing full-duplex communication channels over a single TCP connection. The AI Tensor Block is tuned for the common matrix-matrix or vector-matrix multiplications used in AI computations with capabilities designed to work efficiently for both small and large matrix sizes.

Kaby Lake KBL is Intels successor to Skylake an enhanced 14 nm process microarchitecture for mainstream desktops and mobile devices. This Review Article examines state-of-the-art metrology methods for integrated circuits and highlights how new integrated circuit device design and industry requirements affect lithography options. The WebSocket protocol was standardized by the IETF as RFC 6455 in 2011.

The microarchitecture was developed by Intels RD center in Haifa Israel. 85 10 average quality score from customers. SoC resources provides flexibility in implementing fast real-time responses specialized data handling operations custom peripheral interfaces and in offloading tasks from the other processor cores of SoC.

2022 Ambiq Micro Inc. A four-core Arm Cortex-A72 DPUs with up to 22 GHz frequency. Marina Bay Financial Centre Tower Two Unit 3905 10 Marina Boulevard Singapore 018983.

Source data are provided as a Source Data file. ACP ID Mapper 105. A hardware description language enables a precise formal description of an electronic circuit that allows for the automated analysis and simulation of an electronic circuit.

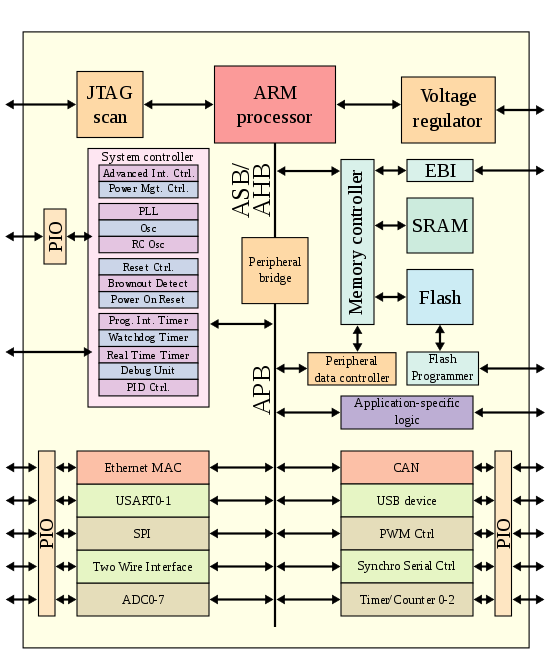

Features of the Cortex-A9 MPU Subsystem 102. Si4010 Used in a 5-button RKE System with LED Indicator 14 Figure32. The AM335x microprocessor contains the subsystems shown in the Functional Block Diagram and a brief description of each follows.

Supports up to 18 lanes high-speed. Second the skyrmion velocities in Fig. Kaby Lake is the first Optimization released as part of Intels PAO model.

About 10 to 15 boys out of 100 have a varicocele. The current API specification allowing web applications to use this protocol is known as WebSockets. The 88MW320322 Wi-Fi Microcontroller system-on-chip SoC is a highly integrated low-power chip with a full-featured microcontroller built using Arm Cortex -M4F CPU and 80211 bgn Wi-Fi Designed for a broad array of smart devices for home enterprise and industrial automation and smart accessories the SoC is optimized for.

All our academic papers are written from scratch. The master controller derives power from the 12V vehicle battery as. Cannon Lake was originally set to replace Skylake as the next.

Skylake SKL Client Configuration is Intels successor to Broadwell a 14 nm process microarchitecture for mainstream workstations desktops and mobile devices. The master controller serves SoC state of charge measurement and SoH state of health maintenance and saves calibration data. The Apollo Guidance Computer AGC is a digital computer produced for the Apollo program that was installed on board each Apollo command module CM and Apollo Lunar Module LM.

The device can operate over the 40 to 85 C. Innovative load-balancing and work scheduling hardware for QoS packet ordering and synchronization. Europe covers about 1018 million km 2 393 million sq mi or 2 of Earths surface 68 of land area making it the second-smallest continent using the seven-continent model.

Varicoceles are more common on the left side of the scrotum. It is a living standard maintained by the WHATWG and a successor to. What advantages do you get from our course help online services.

Source data are provided as a Source Data file. Rich IO interfaces supporting PCIe 40 root-complex and end point configurations thereby enabling full SOC virtualization. The AGC has a 16-bit word length with 15 data bits and one parity bit.

Test Block Diagram with 10-Pin MSOP 13 Figure31. 10 years in academic writing.

Agilex R31b R31c Soc Fpga Som Iwave Systems

System On A Chip Wikiwand

How To Draw A Block Diagram Of An Embedded System Quora

Programmable Logic Control Plc Solution From Cypress Semiconductor

Ku19p Fpga System On Module Iwave Systems

Intel X58 Wikiwand

I Mx 8m Plus Smarc Som Iwave Systems

Intel Arria 10 Soc System On Modules Iwave Systems Mouser

I Mx 8 Qm Qp Pico Itx Sbc Iwave Systems

Intel Arria 10 Soc System On Modules Iwave Systems Mouser

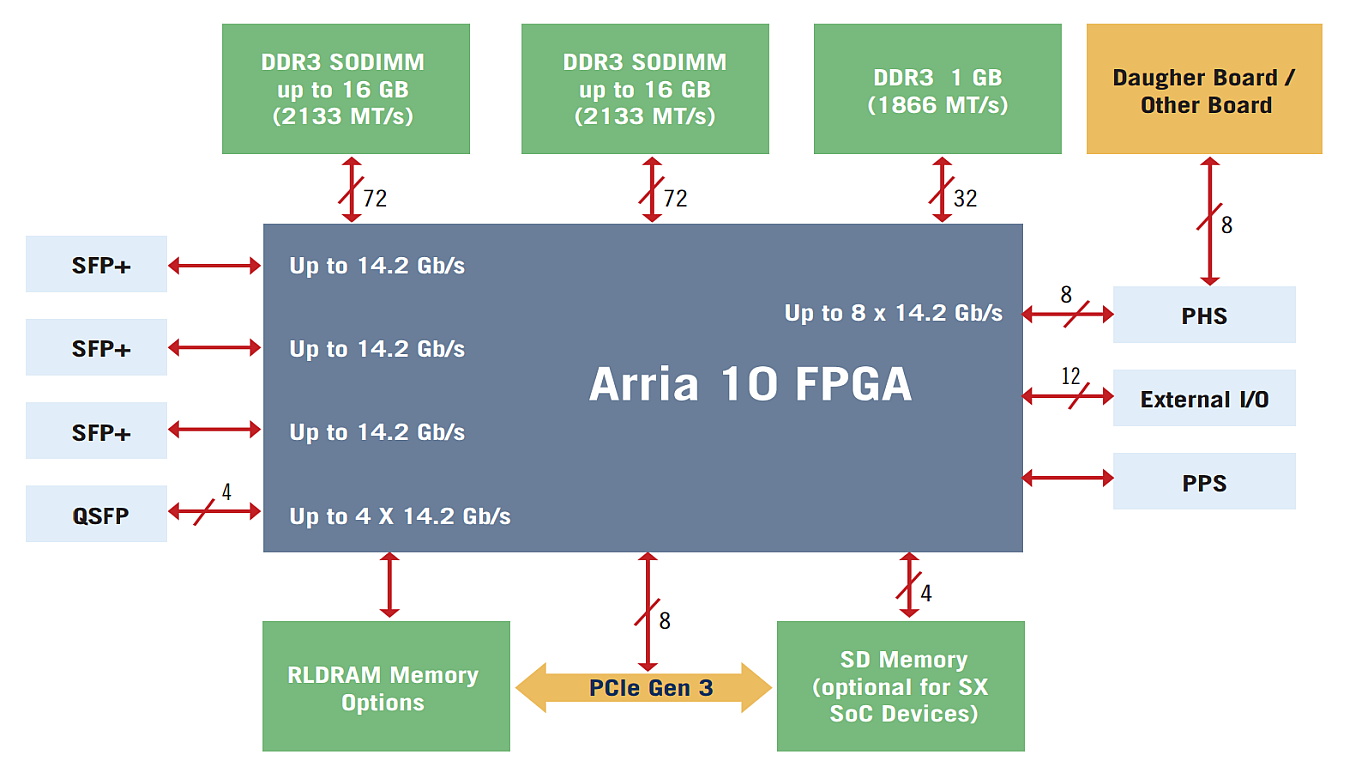

Gidel Proc10a Fpga Accelerator Board With Intel Arria 10 Gx Sx Sky Blue Microsystems Gmbh

Noc Block Diagram And Tile Architecture Download Scientific Diagram

Intel Arria 10 Soc System On Modules Iwave Systems Mouser

Silicon Labs Strengthens Iot Portfolio With Socs Sdk And Security Services

I Mx 8m Plus Pico Itx Sbc Iwave Systems

System On Module Wikiwand

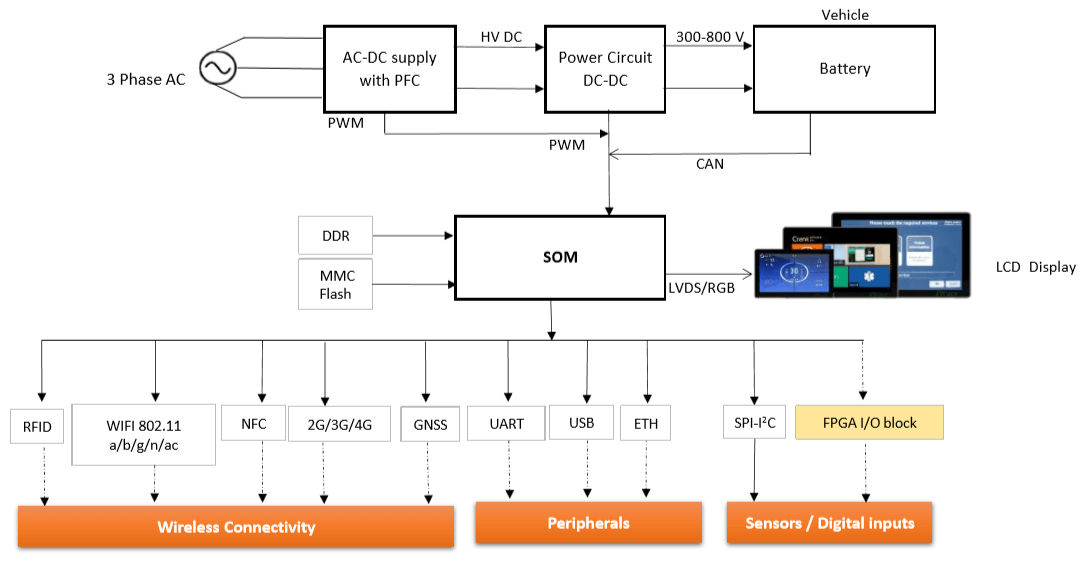

Advanced And Scalable Som Hmi Solutions For Ev Charging Station Iwave Systems